# TEACHING AND LEARNING MATERIAL

# SUBJECT:DIGITAL ELECTRONICS SEMESTER:3<sup>RD</sup>

SUBMITTED BY:-ER. SURABHI TRIPATHY

## **UNIT-1**

## **NUMBER SYSTEM & CODES**

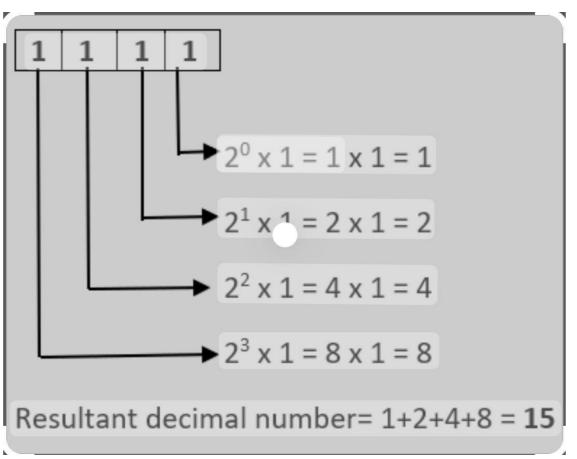

| Binary<br>Number             | 1              | 0  | 1              | 1              | 0              | 1              | Decimal<br>Number |

|------------------------------|----------------|----|----------------|----------------|----------------|----------------|-------------------|

| Power of<br>base             | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |                   |

| Decimal equivalent           | 32             | 16 | 8              | 4              | 2              | 1              |                   |

| Magnitude<br>of each<br>term | 32             | 0  | 8              | 4              | 0              | 1              | 45                |

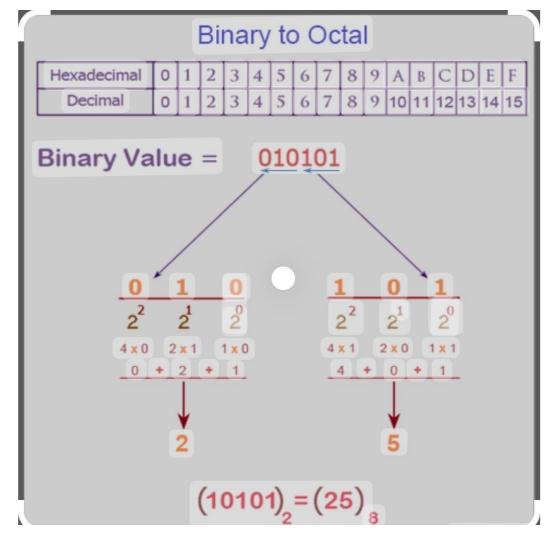

## Octal Number System

- The base is 8.

- Symbols: 0, 1, 2, 3, 4, 5, 6, and 7.

- Positional weights :

$$8^0 = 1$$

$$8^1 = 8$$

$$8^2 = 64$$

$$8^3 = 256$$

$$8^{-1} = 1/8$$

$$8^{-2} = 1/64$$

$$8^{-3} = 1/256$$

| OCTAL    | BINARY                                        |

|----------|-----------------------------------------------|

| 01234567 | 000<br>001<br>010<br>011<br>100<br>101<br>110 |

| Decimal | Binary | Hexadecimal |

|---------|--------|-------------|

| 0       | 0000   | 0           |

| 1       | 0001   | 1           |

| 2       | 0010   | 2           |

| 3       | 0011   | 3           |

| 4       | 0100   | 4           |

| 5       | 0101   | 5           |

| 6       | 0110   | 6           |

| 7       | 0111   | 7           |

| 8       | 1000   | 8           |

| 9       | 1001   | 9           |

| 10      | 1010   | A           |

| 11      | 1011   | В           |

| 12      | 1100   | С           |

| 13      | 1101   | D           |

| 14      | 1110   | E           |

| 15      | 1111   | F           |

# 1110011100010000

E710

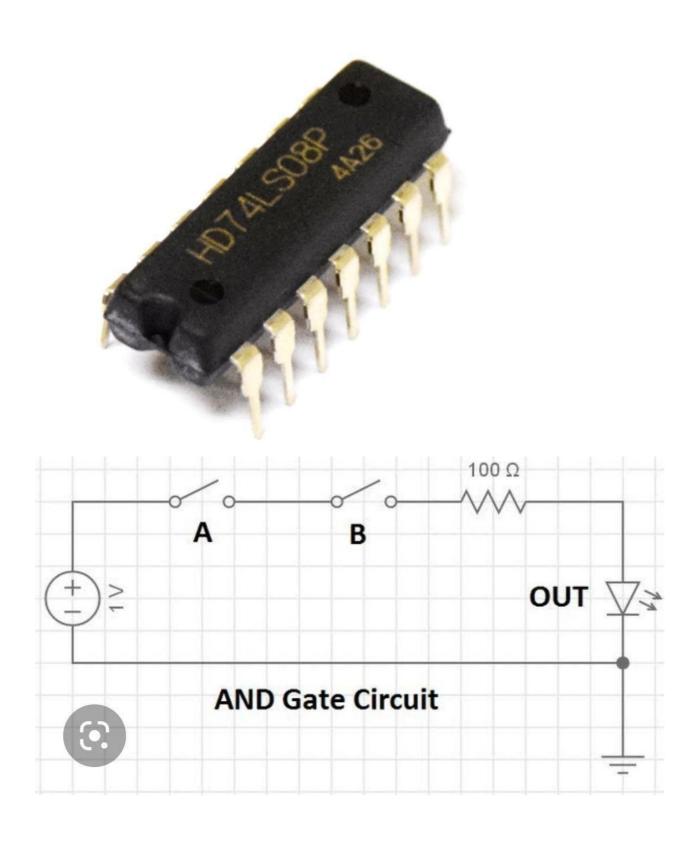

| Name                               | Graphic<br>symbol                           | Algebraic<br>function             | Truth<br>table                            |

|------------------------------------|---------------------------------------------|-----------------------------------|-------------------------------------------|

| AND                                | х                                           | $F = x \cdot y$                   | x y F<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1 |

| OR                                 | <i>x</i>                                    | F = x + y                         | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1 |

| Inverter                           | <i>x</i> —— <i>F</i>                        | F = x'                            | x F<br>0 1<br>1 0                         |

| Buffer                             | <i>x</i> — <i>F</i>                         | F = x                             | x F<br>0 0<br>1 1                         |

| NAND                               | х<br>у                                      | $F = (xy)^*$                      | x y F<br>0 0 1<br>0 1 1<br>1 0 1<br>1 1 0 |

| NOR                                | х<br>у ———————————————————————————————————— | F = (x + y)'                      | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0 |

| Exclusive-OR<br>(X OR)             | x                                           | $F = xy' + x'y$ $= x \oplus y$    | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 0 |

| Exclusive-NOR<br>or<br>equivalence | *F                                          | $F = xy + x'y'$ $= (x \oplus y)'$ | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 1 |

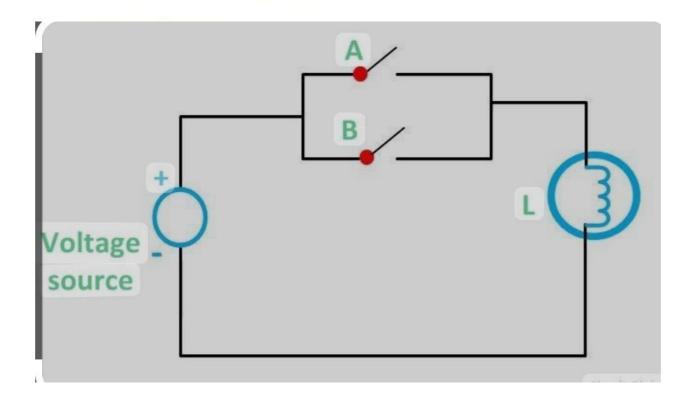

## 2-input AND gate

2-input OR gate

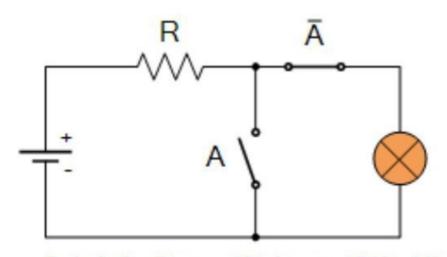

**NOT Gate**

Switch A - Open = "0", Lamp - ON = "1" Switch A - Closed = "1", Lamp - OFF = "0"

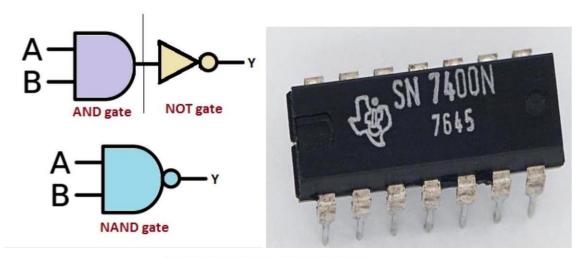

NAND GATE

## NAND GATE

**Electrical Circuit**

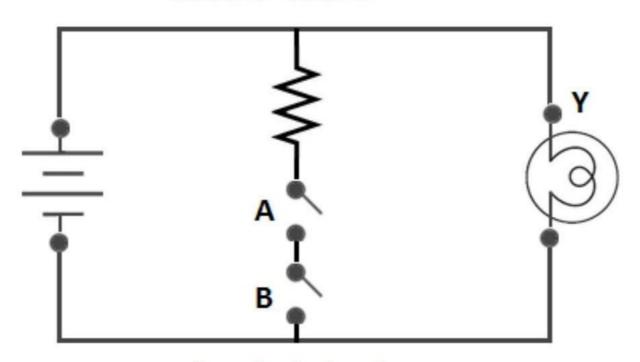

NOR GATE

# NOR GATE A B Electrical Circuit

#### NOR Gate DIP14

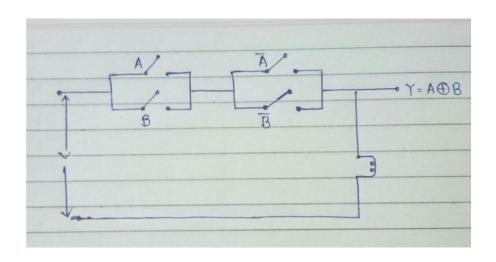

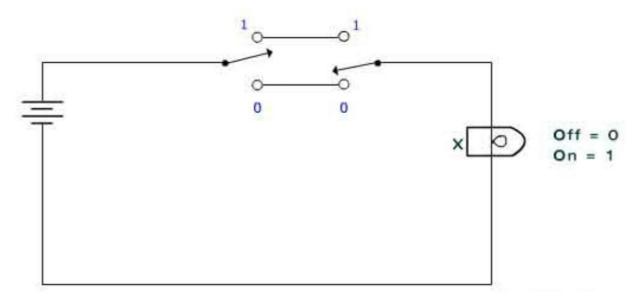

EX-OR GATE

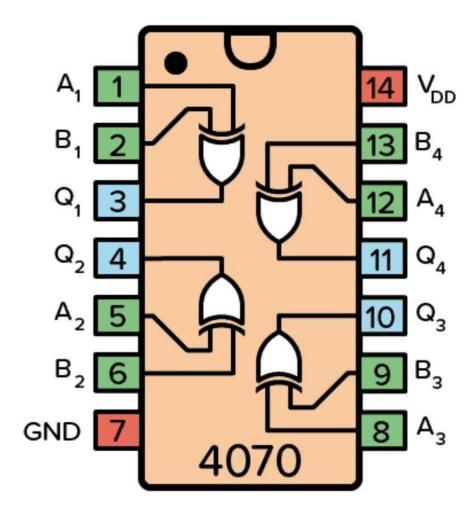

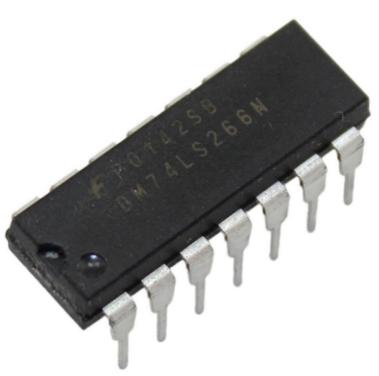

EX-NOR GATE

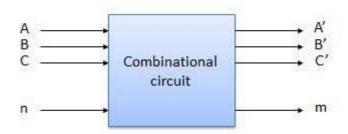

# UNIT-2 COMBINATIONAL CIRCUITS

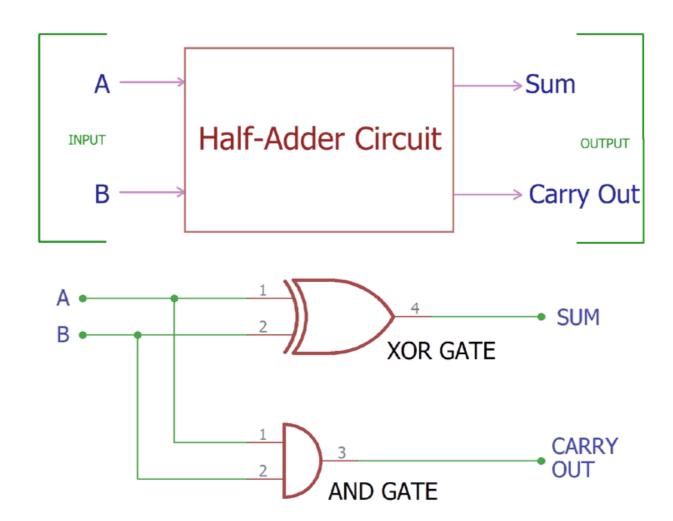

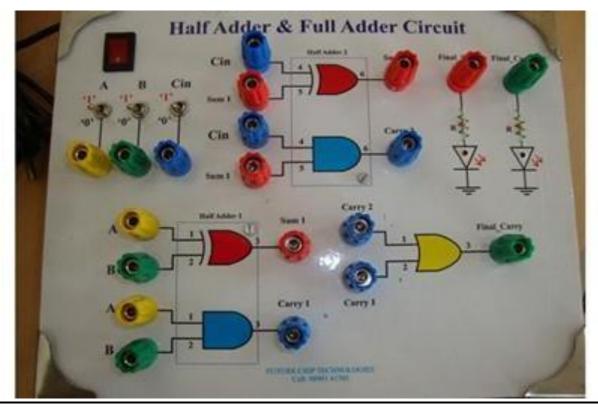

#### **HALF ADDER**

| Truth Table |     |        |       |  |  |

|-------------|-----|--------|-------|--|--|

| Inj         | out | Output |       |  |  |

| A           | В   | Sum    | Carry |  |  |

| 0           | 0   | 0      | 0     |  |  |

| 0           | 1   | 1      | 0     |  |  |

| 1           | 0   | 1      | 0     |  |  |

| 1           | 1   | 0      | 1     |  |  |

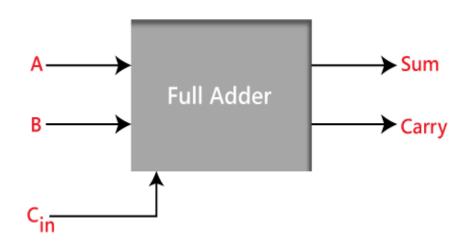

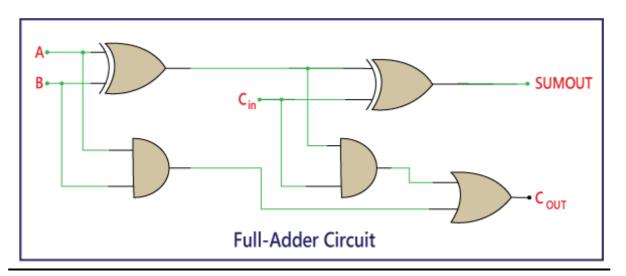

|   | Inputs | Out | puts |       |

|---|--------|-----|------|-------|

| Α | В      | Cin | Sum  | Carry |

| 0 | 0      | 0   | 0    | 0     |

| 0 | 0      | 1   | 1    | 0     |

| 0 | 1      | 0   | 1    | 0     |

| 0 | 1      | 1   | 0    | 1     |

| 1 | 0      | 0   | 1    | 0     |

| 1 | 0      | 1   | 0    | 1     |

| 1 | 1      | 0   | 0    | 1     |

| 1 | 1      | 1   | 1    | 1     |

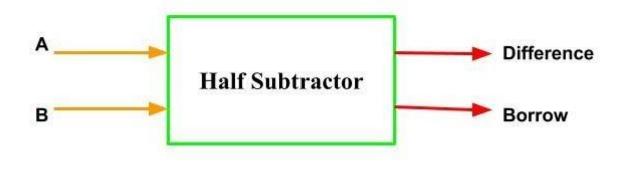

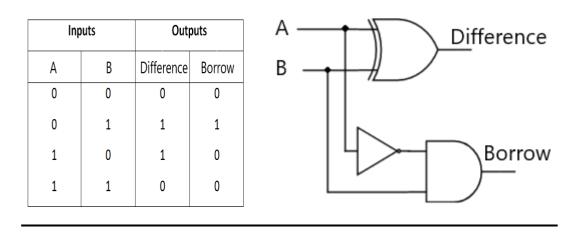

## **HALF SUBTRACTOR**

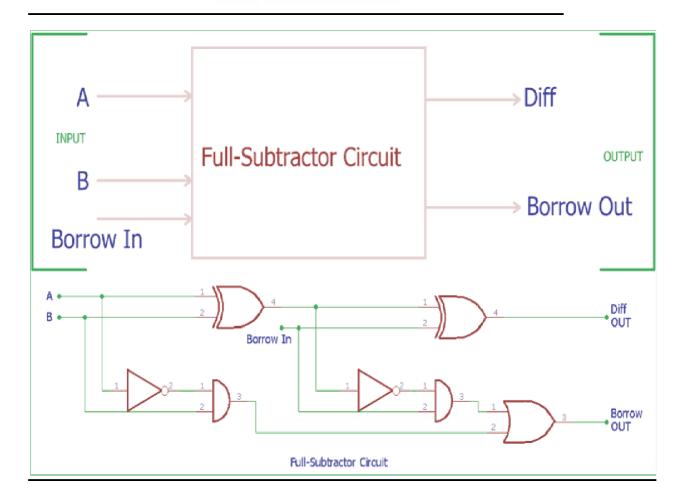

## **FULL SUBTRACTOR**

| Input |   |   | Outp       | ut     |

|-------|---|---|------------|--------|

| А     | В | С | Difference | Borrow |

| 0     | 0 | 0 | 0          | 0      |

| 0     | 0 | 1 | 1          | 1      |

| 0     | 1 | 0 | 1          | 1      |

| 0     | 1 | 1 | 0          | 1      |

| 1     | 0 | 0 | 1          | 0      |

| 1     | 0 | 1 | 0          | 0      |

| 1     | 1 | 0 | 0          | 0      |

| 1     | 1 | 1 | 1          | 1      |

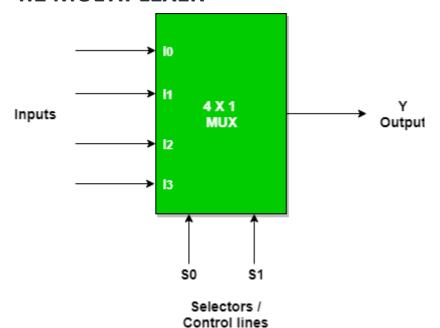

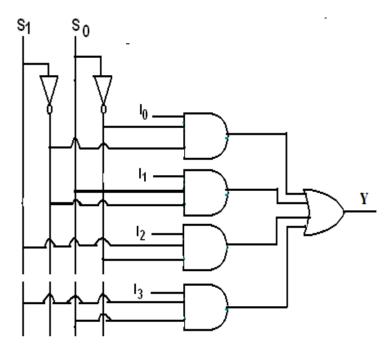

#### **4:1 MULTIPLEXER**

| Input                                                       | S1               | S0               | Y                                                          |

|-------------------------------------------------------------|------------------|------------------|------------------------------------------------------------|

| I <sub>0</sub> I <sub>1</sub> I <sub>2</sub> I <sub>3</sub> | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | ${\rm I}_{0} \\ {\rm I}_{1} \\ {\rm I}_{2} \\ {\rm I}_{3}$ |

$$Y = S_1S_0I_3 + S_1\overline{S_0}I_2 + \overline{S_1}S_0I_1 + \overline{S_1}\overline{S_0}I_0$$

# 4 to 1 Multiplexer and its truth table

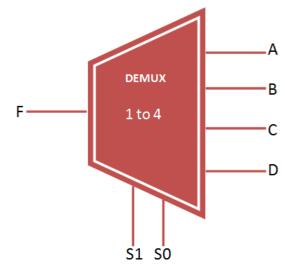

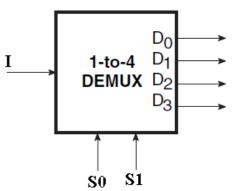

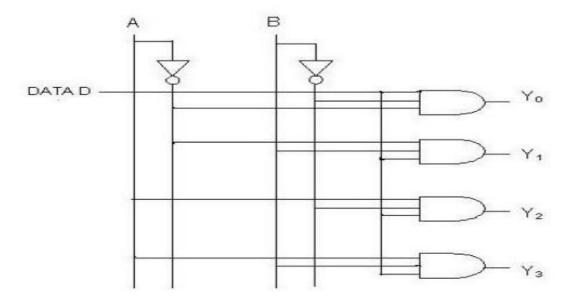

#### 1:4 DEMULTIPLEXER

| т | Sel | ect |                | O/             | Р              |    |

|---|-----|-----|----------------|----------------|----------------|----|

| 1 | SO  | S1  | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D3 |

| 1 | 0   | 0   | 1              | 0              | 0              | 0  |

| 1 | 0   | 1   | 0              | 1              | 0              | 0  |

| 1 | 1   | 0   | 0              | 0              | 1              | 0  |

| 1 | 1   | 1   | 0              | 0              | 0              | 1  |

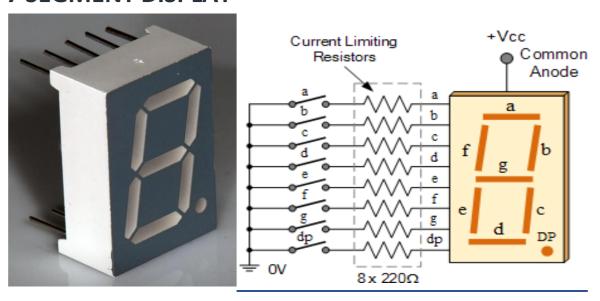

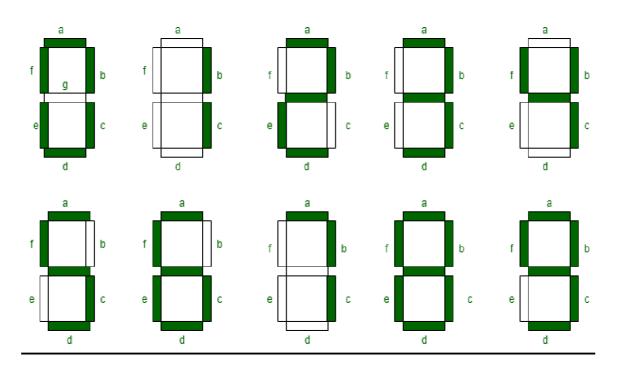

#### **7 SEGMENT DISPLAY**

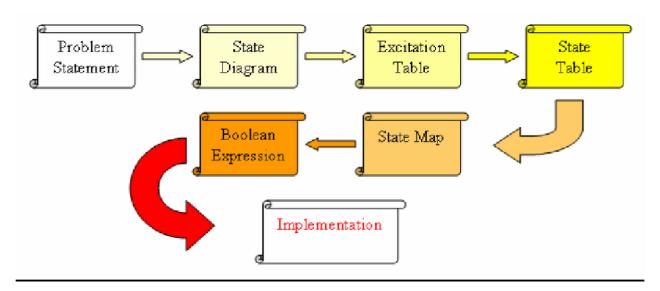

### UNIT-3

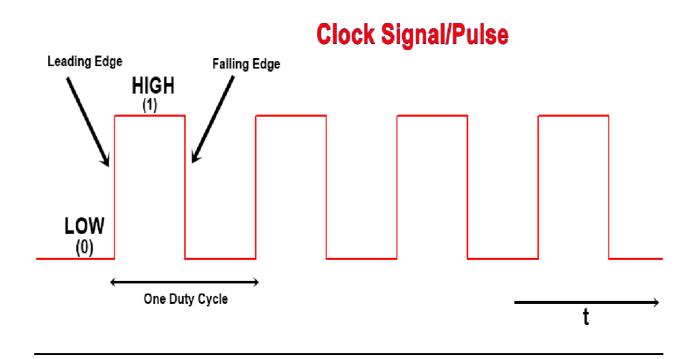

#### **SEQUENTIAL CIRCUIT**

## SR Flip-Flop

| State   | S | R | Q | Q' | Description |

|---------|---|---|---|----|-------------|

| Set     | 1 | 0 | 0 | 1  | Set Q'>>1   |

|         | 1 | 1 | 0 | 1  | No change   |

| Reset   | 0 | 1 | 1 | 0  | Reset Q'>>0 |

|         | 1 | 1 | 1 | 0  | No change   |

| Invalid | 0 | 0 | 1 | 1  | Invalid     |

|         |   |   |   |    | Condition   |

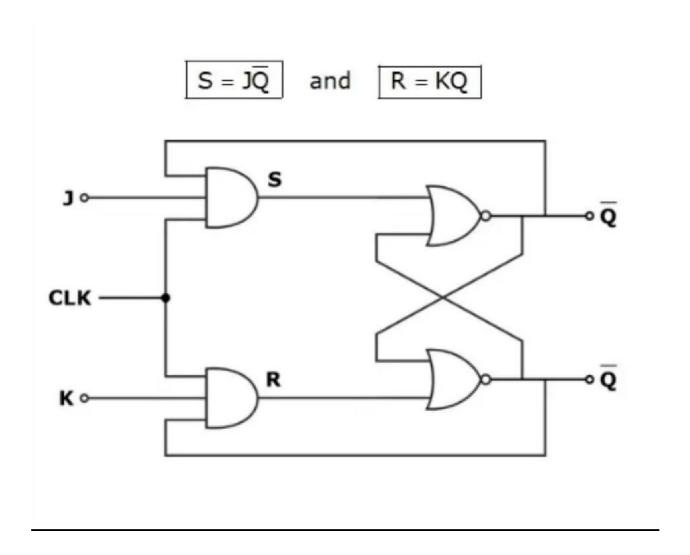

# JK Flip-Flop

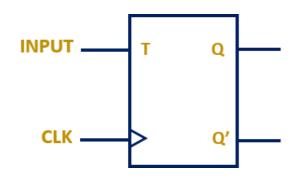

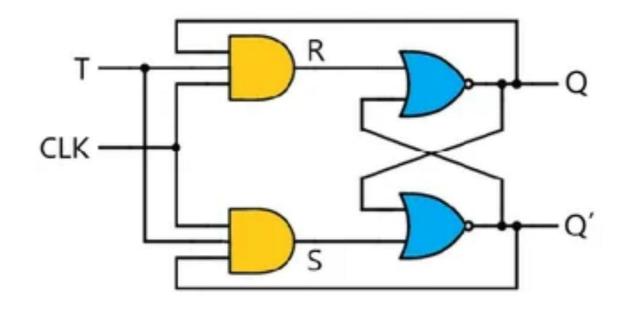

# T Flip-Flop

| Clock | J | K | Q <sub>n+1</sub> | State  |

|-------|---|---|------------------|--------|

| 0     | X | X | Q <sub>n</sub>   |        |

| 1     | 0 | 0 | $Q_n$            | Hold   |

| 1     | 0 | 1 | 0                | Reset  |

| 1     | 1 | 1 | 1                | Set    |

| 1     | 1 | 1 | $\overline{Q}_n$ | Toggle |

# **T FLIP-FLOP**

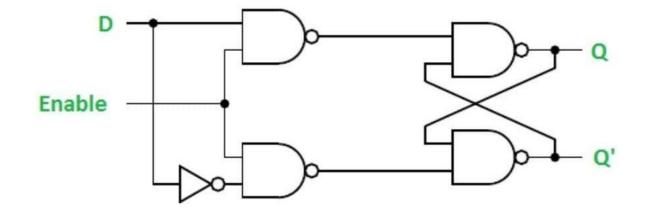

## **D FLIP-FLOP**

## Truth Table for the D-type Flip Flop

| Clock | D | Q | Q' | Description |

|-------|---|---|----|-------------|

| ↓ » 0 | X | Q | Q' | Memory      |

|       |   |   |    | no change   |

| ↑ » 1 | 0 | 0 | 1  | Reset Q » 0 |

| ↑ » 1 | 1 | 1 | 0  | Set Q » 1   |

Symbols ↓ and ↑ indicates the direction of the clock pulse. D-type flip flop assumed these symbols as edge-triggers.